当前位置:首页 → 计算机类 → 软件水平考试 → 中级嵌入式系统设计师->王工在采用某16位嵌入式CPU进行A/D采集硬件电路设计时,

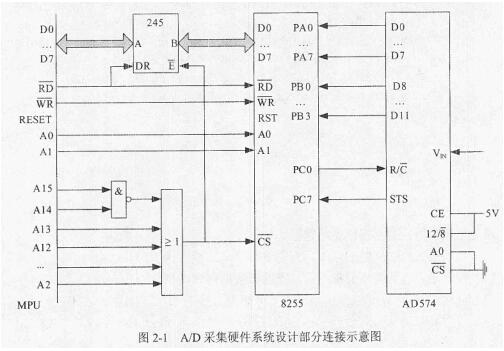

王工在采用某16位嵌入式CPU进行A/D采集硬件电路设计时,利用8255控制器C口中的PC0输出控制信号,利用PC7读入AD574的状态信号,利用A口和B口读入AD574转换好的12位数据。图2-1为该A/D采集硬件系统设计的部分连接示意图。

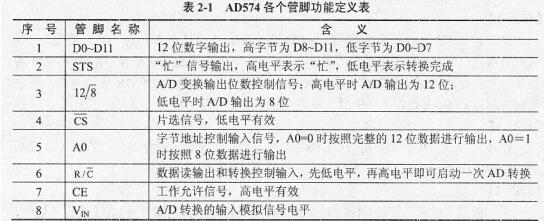

其中,AD574各个管脚功能定义如表2-1所述。

问题2.1、12位

问题2.2、DR=高电平时,A口传向B口;DR=低电平时,B口传向A口。

问题2.3、5v/(4096*2)=0.61mv。

问题2.4、(1)#C003H (2)#C002H(3)#00H(4)#01H(5)#80H(6)#C000H(7)#C001H (8)#0FH

问题2.1、本题考查嵌入式硬件系统设计和基本的汇编程序编写知识。此类题目要求考生认真阅读题目,对题目中给出的原理图、器件描述等内容进行理解,根据原理图中所包含的硬件模块和原理设计,进行问题回答和程序补全。题目给出了主要器件的管脚功能描述和部分程序。

在该嵌入式系统设计中,AD574是工作在12位转换模式还是8位转换模式依赖于AD574周边的管脚电路设计。从题目中已经给出的器件功能描述并结合原理图进行推断。从题目给出的器件描述中可以看出,根据AD574的A0管脚确定12位/8位模式,从原理图可以看出,A0接地,即低电平。结合AD574的功能描述,可以知道该系统设计中AD574工作在12位模式。

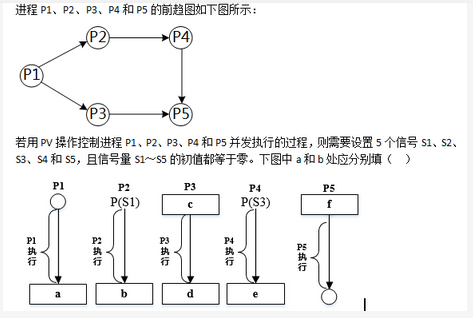

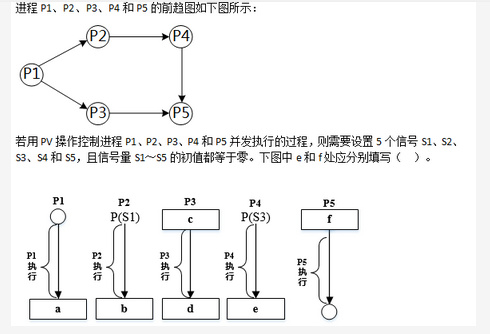

问题2.2、图2-1中245为双向缓冲器,在该硬件设计中配置8255控制字时,CPU需要向245进行数据输出(245的A口传输给B口);在获取AD采集数据时CPU需要接收245所传输过来的数据(245的B口传输给A口)。根据硬件设计图可以看出,当DR为高电平时,RD信号是无效的,也就是读信号无效,即此时为写信号有效。

在写信号有效情况下,数据传输方向是从处理器向8255方向进行数据传输,即从A口传输给BP。反之如果RD为低电平时,此时RD信号有效,也就是读信号有效,既需要从外部将数据读入到CPU处理器中,即从8255进行数据读取,放到处理器中,所以方向应该是从B口传输到A口。

问题2.3、由于工作在12位,其范围为4096个刻度。另外考虑到采用1/2LSB作为量化误差,所以误差大小即为:5v/(4096*2)=0.61mv。

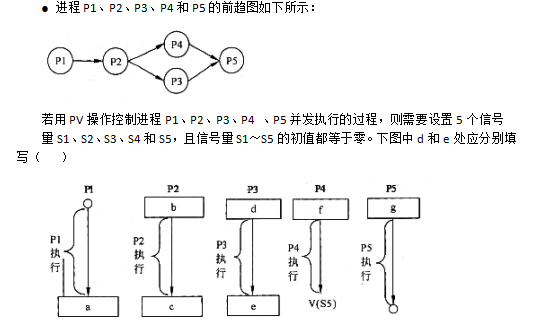

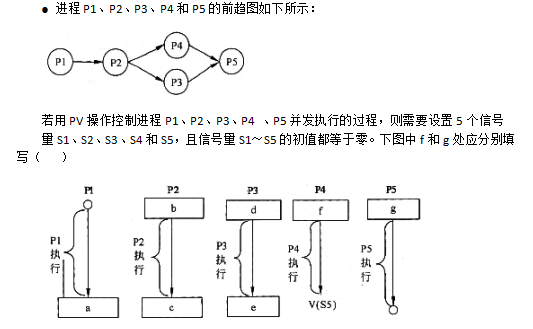

问题2.4、运行数据采集程序时,首先需要对8255进行初始化,然后进行数据采集。在该程序中,需要先进行8255的工作模式配置,由原理图和8255的工作模式可知,在该配置情况下,必须使得8255的A1A0=11,即工作在寻址控制器模式下,同时保证8255的片选有效,即必须使得A15=A14=1,A13=A12=All=…=A2=0才可以,所以此时需要给DPTR寄存器的地址为#C003H。

在进行数据采集过程中,需要先通过8255的C口进行AD574的转换控制,要对C口操作即需要A1A0=10,再考虑到片选的有效性,需要给DPTR的地址是#C002H。在进行一次数据转换时需要在PCO产生一个上升沿,所以要给C口输出配置为#00H和#01H。当从C口取出状态字后,需要借助C口的最高位STS进行转换完毕的状态判断,因此取出数据存在A寄存器后,需要和#80H进行与操作来判断最高位的完成状态。

当判断有有效数据时候,需要分别从8255的A口和B口进行数据的获取,因此需要分别配置A口和B口的地址,依次为#C000H和#C001H。在进行12位数据合并时,只需要通过与操作取出低4位数据,和#OFH进行与操作即可。