当前位置:首页 → 计算机类 → 软件水平考试 → 中级嵌入式系统设计师->某公司承接了一个数据采集与处理系统的项目,由刘工负责系统的方

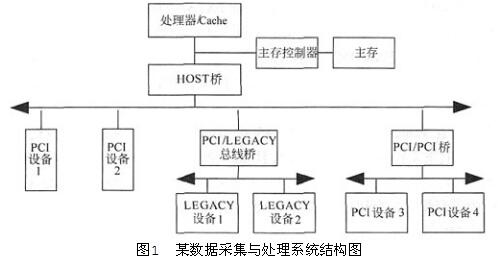

某公司承接了一个数据采集与处理系统的项目,由刘工负责系统的方案设计,刘工的设计方案如图1所示。该方案是基于PCI总线的多功能处理系统,PCI设备1是以太网,PCI设备2用于数据采集,PCI设备3、PCI设备4用于和该系统中的其他处理模块进行互联,LEGACY设备1、LEGACY设备2用于处理系统中一些慢速设备。

1、在以下描述PCI总线的基本概念中,正确的表述有______、______、______、______、______、______。 A.PCI总线是一个与处理器有关的高速外围总线 B.PCI总线的基本传输机制是猝发式传送 C.PCI设备一定是主设备 D.PCI的物理地址与其他总线一样,是由内存地址空间和I/O地址组成 E.PCI设备的地址译码不能对配置空间直接寻址 F.PCI设备识别主要是对开发商代码和设备代码进行识别 G.访问配置空间时,PCI桥应提供IDSEL信号以选择PCI设备 H.系统中只允许有一条PCI总线 I.PCI总线是高速串行总线 J.PCI总线有3种桥,即HOST/PCI桥,PCI/PCI桥,PCI/LEGACY桥 K.PCI桥是可以把一条总线的地址空间映射到另一条总线的地址空间

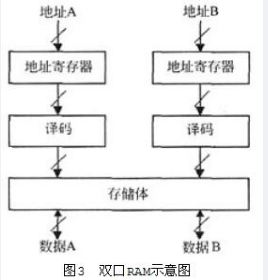

2、PCI设备2和主CPU之间采用双口RAM方式交换数据,双口RAM是常见的共享式多端口存储器,其最大的特点是存储数据共享。它允许两个独立的CPU或控制器同时异步访问存储单元。既然数据共享,就必须存在访问仲裁控制,否则就会出现错误或冲突。内部仲裁逻辑控制提供以下功能:对同一地址单元访问的时序控制;存储单元数据块的访问权限分配;信令交换逻辑(例如中断信号)等。

两个端口对同一内存操作有4种情况:A.两个端口同时对同一地址单元读出数据;B.两个端口同时对同一地址单元写入数据;C.两个端口不同时对同一地址单元存取数据;D.两个端口同时对同一地址单元,一个写入数据,另一个读出数据。

在上述情况下,两个端口的存取不会出现错误的是______和______,会出现写入错误的是______,会出现读出错误的是______。

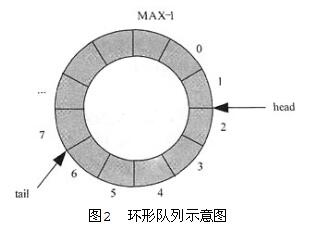

3、PCI设备2和主CPU之间通过双端口存储器进行数据交换。刘工设计了环形队列的实现方式。设备2向环形队列写入数据,主CPU从环形队列读取数据。环形队列是一个首尾相连的FIFO数据结构,采用数组存储,到达尾部时将转回到0位置,该转回是通过取模操作来实现的。因此环形队列逻辑上是将数组元素q[0]与q[MAX-1]连接,形成一个存放队列的环形空间。为了方便读写,还要用数组下标来指明队列的读写位置,其中head指向可以读的位置,tail指向可以写的位置,环形队列如图2所示。

使用环形队列时需要判断队列为空还是为满。当tail追上head时,队列为满,当head追上tail时,队列为空。通常判断环形队列为空/为满有两种判断方法。

(1)附加一个标志位tag,当head赶上tail,队列空,则令tag=0,当tail赶上head,队列满,则令tag=1;

(2)限制tail赶上head,即队尾结点与队首结点之间至少留有一个元素的空间。队列空:head==tai;队列满:(tail+1)%MAXN==head。

如果采用第一种方法(即附加标志实现算法),则环形队列的结构定义如下: typedef struct ringg { int head; /*头部,出队列方向*/ int tail; /*尾部,入队列方向*/ int tag; int size; /*队列总尺寸*/ int space[RINGQ_MAX]; /*队列空间*/ }RINGQ; RINGQ p, *q; q=&p; 初始化环形队列的C语言代码为: q->head=q->tail=q->tag=0; q->size=RINGQ_MAX; 判断队列为空的C语言代码为______。判断队列为满的C语言代码为______。入队操作时,如果队列不满,则入队后更新尾指针的C语言代码为q->tail=______。出队操作时,如果队列不空,则出队后更新头指针的C语言代码为q->head=______。如果采用第二种方法,还采用上述数据结构,初始化环形队列的C语言代码为:q->head=q->tail=0; q->size=RINGQ_MAX; 判断队列为空的C语言代码为______。 判断队列为满的C语言代码为______。 入队操作时,如果队列不满,则入队后更新尾指针的C语言代码为q->tail=______。 出队操作时,如果队列不空,则出队后更新头指针的C语言代码为q->head=______。

1、B、E、F、G、J、K

2、A C B D

3、(q->head==q->tail)&&(q->tag=0) ((q->head=q->tail)&&(q->tag==1)) (q->tail+1)%q->size (q->head+1)%q->size (q->head==q->tail) (q->head==(q->tail+1)%q->size)) (q->tail+1)%q->size (q->head+1)%q->size

1、本题考查嵌入式系统中计算机总线、存储、环形队列等相关知识。

该方案是基于PCI总线的多功能处理系统。PCI(Peripheral Component Interconnect)总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。在数字图形、图像和语音处理,以及高速实时数据采集与处理等对数据传输率要求较高的应用中,采用PCI总线来进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。

PCI总线是一种树型结构,并且独立于CPU,可以和CPU并行操作。PCI总线上可以挂接PCI设备和PCI桥片,一个PCI设备可以既是主设备也是从设备,但是在同一个时刻,这个PCI设备或者为主设备或者为从设备。在PCI总线中有3类设备,PCI主设备、PCI从设备和桥设备。其中PCI从设备只能被动地接收来自HOST主桥,或者其他PCI设备的读写请求;而PCI主设备可以通过总线仲裁获得PCI总线的使用权,主动地向其他PCI设备或者主存储器发起存储器读写请求。而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。PCI总线有3种桥,即HOST/PCI桥、PCI/PCI桥和PCI/LEGACY桥。

PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现猝发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定谁有权力拿到总线的主控权。

PCI总线有如下显著的特点:

(1)高速性,PCI局部总线以33MHz的时钟频率操作,采用32位数据总线,数据传输速率可高达132MB/s,远超过以往各种总线。而早在1995年6月推出的PCI总线规范2.1已定义了64位、66MHz的PCI总线标准。因此PCI总线完全可为未来的计算机提供更高的数据传送率。另外,PCI总线的主设备(Master)可与计算机内存直接交换数据,而不必经过计算机CPU中转,也提高了数据传送的效率。

(2)即插即用性,PCI设备识别主要是对开发商代码和设备代码进行识别,PCI设备的硬件资源,则是由计算机根据其各自的要求统一分配,绝不会有任何的冲突问题。作为PCI板卡的设计者,不必关心计算机的哪些资源可用,哪些资源不可用,也不必关心板卡之间是否会有冲突。

(3)可靠性,PCI独立于处理器的结构,形成一种独特的中间缓冲器设计方式,将中央处理器子系统与外围设备分开。这样用户可以随意增添外围设备,以扩充计算机系统而不必担心在不同时钟频率下会导致性能的下降。PCI总线增加了奇偶校验错(PERR)、系统错(SERR)、从设备结束(STOP)等控制信号及超时处理等可靠性措施,使数据传输的可靠性大为增加。

(4)复杂性,PCI总线强大的功能大大增加了硬件设计和软件开发的实现难度。硬件上要采用大容量、高速度的CPLD或FPGA芯片来实现PCI总线复杂的功能。软件上则要根据所用的操作系统,用软件工具编制支持即插即用功能的设备驱动程序。

(5)自动配置,PCI总线规范规定PCI设备可以自动配置。PCI定义了3种地址空间:存储器空间、输入/输出空间和配置空间,每个PCI设备中都有256字节的配置空间用来存放自动配置信息,在系统初始化时,通过idsel引脚片选决定PCI设备,自动根据读到的有关设备的信息,结合系统的实际情况为设备分配存储地址、中断和某些定时信息。

(6)共享中断,PCI总线是采用低电平有效方式,多个中断可以共享一条中断线。

(7)扩展性好,如果需要把许多设备连接到PCI总线上,而总线驱动能力不足时,可以采用多级PCI总线,这些总线上均可以并发工作,每个总线上均可挂接若干设备。因此PCI总线结构的扩展性是非常好的。

(8)多路复用,在PCI总线中为了优化设计采用了地址线和数据线共用一组物理线路,即多路复用。PCI接插件尺寸小,又采用了多路复用技术,减少了元件和管脚个数,提高了效率。

(9)严格规范,PCI总线对协议、时序、电气性能、机械性能等指标都有严格的规定,保证了PCI的可靠性和兼容性。由于PCI总线规范十分复杂,其接口的实现就有较高的技术难度。

2、双口RAM是在一个存储器上具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对该存储器进行随机性的访问。每个读写口都有一套自己的地址寄存器和译码电路,可以并行地独立工作。两个读写口可以按各自接收的地址同时读出或写入,或一个写入而另一个读出。

与两个独立的存储器不同,两个读写口的访存空间相同,可以访问同一个存储单元。通常使双端口存储器的一个读写口面向CPU,另一个读写口则面向外设或输入/输出处理机。如图3所示。

双口RAM最大的特点是存储数据共享。一个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。因为数据共享,就必须存在访问仲裁控制。

当两个端口对同一内存操作时,当两个端口同时对同一地址单元读出数据,或者两个端口不同时对同一地址单元存取数据的情况下,两个端口的存取不会出现错误;当两个端口同时对同一地址单元写入数据的情况下,会出现写入错误;当两个端口同时对同一地址单元,一个写入数据,另一个读出数据的情况下,会出现读出错误。

3、环形队列是在实际编程极为有用的数据结构,它有如下特点:它是一个首尾相连的FIFO的数据结构,采用数组的线性空间;数据组织简单,能很快知道队列是否满或空;能以很快的速度来存取数据。因为简单高效,甚至在硬件都实现了环形队列。

内存上没有环形的结构,因此环形队列实际上是数组的线性空间来实现。那当数据到了尾部如何处理呢?它将转回到0位置来处理。这个转回是通过数组下标索引取模操作(Index% MAXN)来实现的。

因此环列队列的是逻辑上将数组元素q[0]与q[MAXN-1]连接,形成一个存放队列的环形空间。为了方便读写,还要用数组下标来指明队列的读写位置。定义Head/tail两个变量,其中head指向可以读的位置,tail指向可以写的位置。

环形队列的关键是判断队列为空,还是为满。当tail追上head时,队列为满;当head追上tail时,队列为空。但如何知道谁追上谁,还需要一些辅助的手段来判断。

如何判断环形队列为空、为满有两种判断方法。一是附加一个标志位tag,当head赶上tail,队列空,则令tag=0,当tail赶上head,队列满,则令tag=1;二是限制tail赶上head,即队尾结点与队首结点之间至少留有一个元素的空间。队列空时head==tail,队列满时(tail+1)%MAXN=head。

入队操作时,如队列不满,则写入q->tail=(q->tail+1)%q->size;出队操作时,如果队列不空,则从head处读出。下一个可读的位置在q->head=(q->head+1)%q->size。

一台主机的IP地址为202.123.25.36,掩码为255.255.254.0。如果该主机需要在该网络进行直接广播,那么它应该使用的目的地址为( )

在计算机系统的日常维护工作中,应当注意硬盘工作时不能__(2)__。另外,需要防范病毒,而__(3)__是不会被病毒感觉的。

有 4 个 IP 地址:201.117.15.254、201.117.17.01、201.117.24.5 和 201.117.29.3,如果子网掩码为 255.255.248.0,则这 4 个地址分别属于3个子网;其中属于同一个子网的是()

在异步通信中,每个字符包含1位起始位、7位数据位、1位奇偶位和1位终止位,每秒钟传送200个字符,采用4相位调制,则码元速率为()。

在 Windows 中,运行( )命令得到下图所示结果。以下关于该结果的叙述中,错误的是( )。

Pinging 59.74.111.8 with 32 bytes of data:

Reply from 59.74.111.8: bytes=32 time=3ms TTL=60

Reply from 59.74.111.8: bytes=32 time=5ms TTL=60

Reply from 59.74.111.8: bytes=32 time=3ms TTL=60

Reply from 59.74.111.8: bytes=32 time=5ms TTL=60

Ping statistics for 59.74.111.8:

Packets: Sent = 4, Received = 4, Lost = 0 (0% loss),

Approximate round trip times in milli-seconds:

Minimum = 3ms, Maximum = 5ms, Average = 4ms

在ISO OSF/RM参考模型中,七层协议中的__(1)__利用通信子网提供的服务实现两个用户进程之间端到端的通信。在这个模型中,如果A用户需要通过网络向B用户传送数据,则首先将数据送入应用层,在该层给它附加控制信息后送入表示层;在表示层对数据进行必要的变换并加头标后送入会话层;在会话层加头标送入传输层;在传输层将数据分解为__(本题)__后送至网络层;在网络层将数据封装成__(3)__后送至数据链路层;在数据链路层将数据加上头标和尾标封装成__(4)__后发送到物理层;在物理层数据以__(5)__形式发送到物理线路。B用户所在的系统接收到数据后,层层剥去控制信息,把原数据传送给B用户。

在OSI/RM中,解释应用数据语义的协议层是()。

在TCP/IP协议栈中,ARP协议的作用是(),RARP协议的作用是(请作答此空)。

在地址 http://www.dailynews.com.cn/channel/welcome.htm 中,www.dailynews.com.cn 表示( ),welcome.htm 表示(请作答此空)。

在电子表格软件Excel中,假设A1单元格的值为15,若在A2单元格输入“=AND(15<A1,A1<100)”,则A2单元格显示的值为 ()