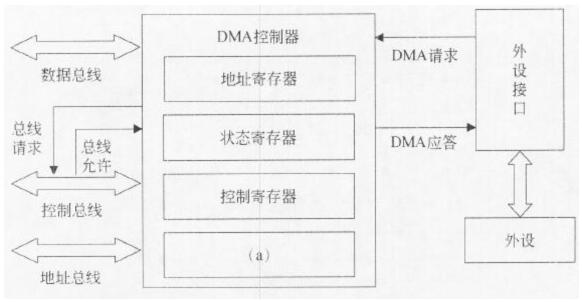

当前位置:首页 → 计算机类 → 软件水平考试 → 中级嵌入式系统设计师->下图为典型直接存储器访问(DMA)控制器结构示意图,图中(a

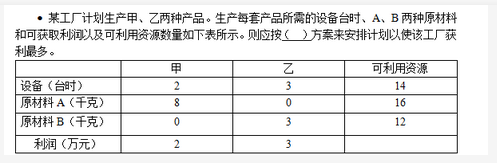

下图为典型直接存储器访问(DMA)控制器结构示意图,图中(a)应为( )。

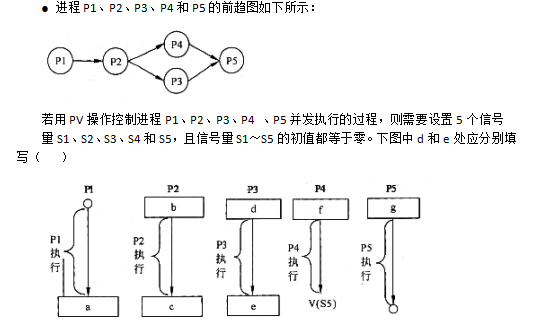

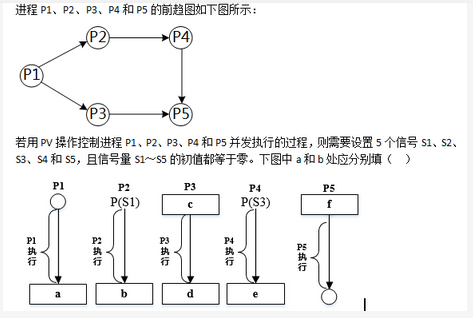

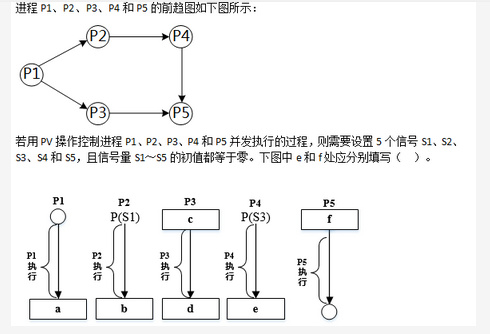

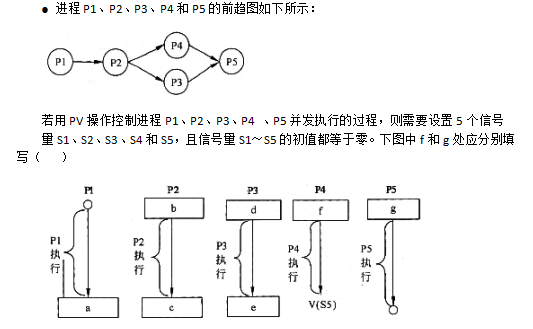

本题考查嵌入式处理器DMA基础知识。直接存储器存取(DMA)控制器是一种在系统内部转移数据独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力外设连接起来控制器。DMA控制器包括一条地址总线、一条数据总线和控制寄存器,一个处理器可以包含多个DMA控制器,每个控f器有多个DMA通道,以及多条直接与存储器和外设连接总线。每个DMA控制器有一组FIFO,起到DMA子系统和外设或存储器之间缓冲器作用。在实现DMA传输时,是由DMA控-器直接掌管总线,因此,存在着一个总线控制权转移问题。即DMA传输前,CPU要把总线控制权交给DMA控制器,而在结束DMA传输后,DMA控制器应立即把总线控制权再交回给CPU。一个完整DMA传输过程必须经过下面4个步骤:1.DMA请求,CPU对DMA控制器初始化,并向I/O接口发出操作命令,I/O接口提出DMA请求。2.DMA响应,DMA控制器对DMA请求判别优先级及屏蔽,向总线裁决逻辑提出总线请求。当CPU执行完当前总线周期即可释放总线控制权。此时,总线裁决逻辑输出总线应答,表示DMA已经响应,通过DMA控制器通知I/O接口开始DMA传输。3.DMA传输,DMA控制器获得总线控制权后,CPU即刻挂起或只执行内部操作,由DMA控制器输出读写命令,直接控制RAM与I/O接口进行DMA传输。在DMA控制器控制下,在存储器和外部设备之间直接进行数据传送,在传送过中不需要中央理器参与。开始时需提供要传送数据起始位置和数据长度。4.DMA结束,当完成规定成批数据传送后,DMA控制器即释放总线控制权,并向I/O接口发出结束信号。当I/O接口收到结束信号后,一方面停止I/O设备工作,另一方面向CPU提出中断请求,使CPU从不介入状态解脱,并执行一段检查本次DMA传输操作正确性代码。